# Replacing Atmel's TS81102G0 DMUX with Atmel's AT84CS001 LVDS DMUX

### Introduction

With the increasing demand for low-power devices, Atmel is introducing a new demultiplexer intended as a companion chip for its high-speed ADCs (TS8388B 8-bit 1 Gsps, TS83102G0B 10-bit 2 Gsps and AT84AS008 10-bit 2.2 Gsps ADCs).

The AT84CS001 is a low-power 10-bit 1:2 or 1:4 2.2 GHz DMUX with LVDS format I/Os for easy interfacing with high-speed FPGAs.

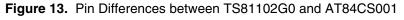

This new DMUX has only minor differences with the TS81102G0 8 or 10-bit 2 GHz 1:4/8 DMUX in terms of I/O access and location, while offering LVDS compatibility and numerous functional improvements.

This document highlights the hardware-related differences between the TS81102G0 and the AT84CS001.

Migration from TS81102G0 to AT84CS001

### Application Note

5413A-BDC-11/04

### Main Differences Between TS81102G0 and AT84CS001 DMUX Devices

The TS81102G0 and AT84CS001 are demultiplexers for use as companion chips with Atmel's high-speed ADCs.

Table 1 highlights the main differences between the two devices.

#### Table 1. Differences between TS81102G0 and AT84CS001 Devices

| Parameter                              | TS81102G0                               | AT84CS001                               |  |

|----------------------------------------|-----------------------------------------|-----------------------------------------|--|

| Data format                            | Selectable 8 or 10-bit                  | 10-bit with additional 11th bit         |  |

| Ratio                                  | 1:4 or 1:8                              | 1:2 or 1:4                              |  |

| Maximum frequency                      | 2 GHz                                   | 2.2 GHz                                 |  |

| Power supplies                         | 5V, -5V, V <sub>PLUSD</sub> (0 to 3.3V) | 3.3V, 2.5V                              |  |

| I/O compatibilities                    | ECL/PECL/TTL/SSTL2                      | LVDS                                    |  |

| Output mode                            | Simultaneous                            | Simultaneous or staggered               |  |

| Input rate mode                        | Single or double data rate (DR or DR/2) | Single or double data rate (DR or DR/2) |  |

| Output rate mode                       | Single data rate (DR)                   | Single or double data rate (DR or DR/2) |  |

| Power dissipation                      | 4 to 9W                                 | 2.6W                                    |  |

| Reset                                  | Asynchronous and synchronous resets     | Asynchronous reset only                 |  |

| Functions:                             |                                         |                                         |  |

| Clock delay adjust                     | Yes                                     | Yes                                     |  |

| Standalone delay cell                  | Yes                                     | Yes                                     |  |

| Swing adjust                           | Yes                                     | No                                      |  |

| Sleep mode                             | No                                      | Yes                                     |  |

| Built-in Test                          | Yes                                     | Yes                                     |  |

| Temperature diode                      | Yes                                     | Yes                                     |  |

| Available package TBGA 240<br>CQFP 196 |                                         | EBGA 240                                |  |

### New Functions of the AT84CS001

|                                 | <ul> <li>In addition to improvements made on the AT84CS001 to minimize its power consumption compared to the TS81102G0, and to simplify interfacing with high-speed FPGAs – in particular thanks to its fully-differential LVDS output compatibility – the AT84CS001 benefits from numerous new functions, including:</li> <li>A selectable output clock mode (single or double rate)</li> <li>A sleep mode, allowing you to reduce the device's power consumption by 60%</li> <li>A staggered mode, providing you with simultaneous or staggered data at the device's output</li> <li>An additional 11th bit, which can be used to process the ADC's out-of-range bit</li> <li>A reset, only one of which is necessary with the AT84CS001 (asynchronous reset)</li> </ul> |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

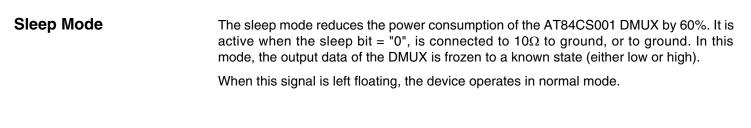

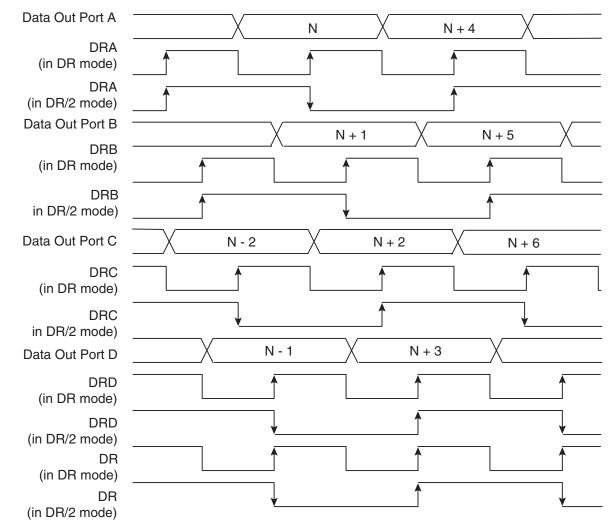

| Selectable Output Clock<br>Mode | <ul> <li>There are two selectable modes for the type of output clock:</li> <li>DR mode: only the output clock's rising edge is active and the output clock rate is the same as the output data rate</li> <li>DR/2 mode: both the output clock's rising and falling edges are active and the output clock rate is half the output data rate.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 1. DR Mode               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DR<br>Data Out                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2. DR/2 Mode             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DR<br>Data Out                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Table 2. | DMUX | Output | Clock | Туре | Selection | Settings |

|----------|------|--------|-------|------|-----------|----------|

|----------|------|--------|-------|------|-----------|----------|

| DRTYPE | DMUX Output Clock Type |

|--------|------------------------|

| 1      | DR                     |

| 0      | DR/2                   |

Note: When DRTYPE is left floating, the default mode is DR/2.

### **Staggered Mode**

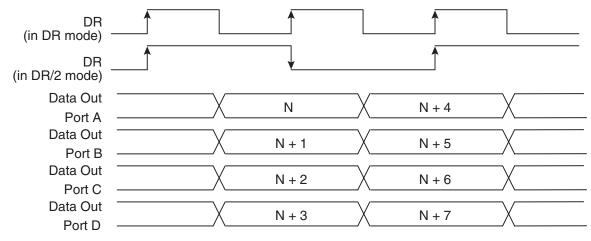

Two output modes are provided:

- Staggered, where the data packets are output one after the other. This mode is activated through the STAGG signal (active at low level when = "0"). When STAGG is left floating, the simultaneous mode is activated.

- Simultaneous, where all data packets are output at the same time (default mode).

### Figure 3. Simultaneous Mode

Figure 4. Staggered Mode (1:2 Ratio)

### Figure 5. Staggered Mode (1:4 Ratio)

### **Additional Bit**

When a signal is applied on IOR and IORN, the "additional bit" is activated. It can be used to process the out-of-range bit from the ADC and plays the role of the 11th bit in the case of a 10-bit stream.

In 1:2 ratio, AOR, DRAN and BOR, DRBN output this signal at half its initial speed (IOR, IORN is demultiplexed by the DMUX ratio).

In 1:4 ratio, AOR, DRAN, BOR, DRBN, COR, DRCN and DOR, DRDN output this signal at a quarter of its initial speed.

In staggered output mode, AOR, DRAN, BOR, DRBN, COR, DRCN and DOR, DRDN output a Data Ready signal for each port, centered on the corresponding data, in which case the additional bit is disabled.

### 6 Migration from TS81102G0 to AT84CS001

#### Reset

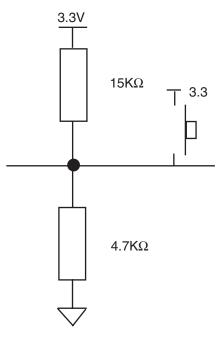

With regard to the AT84CS001 DMUX, only one master reset – the asynchronous reset – is available and necessary. This reset is required to start the device and acts as master reset of the DMUX.

The AT84CS001 does not require any synchronous reset. In the case of multichannel operation, synchronization of all ADCs and DMUXes is guaranteed by resetting both the ADC and the DMUX.

The asynchronous reset is active on high level (3.3V). When the ASYNCRST signal is grounded the device is not in reset state.

Figure 6. Possible Implementation of Asynchronous Reset

During an asynchronous reset, the input clock of the DMUX must be stopped at low level in order to satisfy timing constraints (this condition is met when Atmel's single ADCs are in reset, in which case the Data Ready signal is held low).

The ASYNCRST signal frequency should be 200 MHz maximum.

Note: When the functions (RSTYPE, STAGG, BIST) change, we must apply an ASYNCRST signal to start out with the appropriate configuration.

### **Electrical Characteristics**

The TS81102G0 was designed using a high-speed bipolar process requiring -5V and 5V power supplies whereas the AT84CS001 was designed using a 3.3V BiCMOS process. This difference has many implications on both devices in terms of electrical characteristics.

The following table focuses on changes in the signal electrical levels when migrating from one device to the other.

Table 3. Signal Electrical Levels

| Туре            | TS81102G0          |                                          | AT840                                             | CS001                                    | Description                                                      |  |

|-----------------|--------------------|------------------------------------------|---------------------------------------------------|------------------------------------------|------------------------------------------------------------------|--|

|                 | Name               | Level                                    | Name                                              | Level                                    |                                                                  |  |

| Digital inputs  | 10/10b19/19b       | Differential ECL                         | 10/10N19/19N                                      | LVDS                                     | Input data<br>On-chip 100Ω differential<br>termination           |  |

|                 |                    |                                          | IOR/IORN                                          | LVDS                                     | Additional input bit<br>On-chip 100Ω differential<br>termination |  |

|                 | CLK/CLKb           | Differential ECL                         | CLK/CLKN                                          | LVDS                                     | Input clock<br>On-chip 100Ω differential<br>termination          |  |

| Digital outputs | A0A9<br>to<br>H0H9 | Adjustable single logic                  | A0/A0NA9/A9N<br>to<br>D0/D0ND9/D9N                | LVDS                                     | Output data                                                      |  |

|                 | Ref A Ref B        | Reference signal for each port           | AOR/DRAN,<br>AORN/DRA to<br>DOR/DRDN,<br>DORN/DRD | LVDS                                     | Additional output bits or<br>output clock in staggered<br>mode   |  |

|                 | DR/DRb             | Adjustable<br>differential logic         | DR/DRN                                            | LVDS                                     | Output clock                                                     |  |

| Control signals | ClkInType          | TTL                                      | CLKTYPE                                           | "1": R = 10 KΩ<br>"0": R= 10Ω            | Input clock mode                                                 |  |

|                 |                    |                                          | DRTYPE                                            | "1": R = 10 KΩ<br>"0": R= 10Ω            | Output clock mode                                                |  |

|                 | NbBIT              | TTL                                      | (Suppressed)                                      |                                          | Number of bit selection                                          |  |

|                 |                    |                                          | SLEEP                                             | "1": R = 10 KΩ<br>"0": R= 10Ω            | Sleep mode                                                       |  |

|                 |                    |                                          | STAGG                                             | "1": R = 10 KΩ<br>"0": R= 10Ω            | Staggered mode                                                   |  |

|                 | RatioSel           | TTL                                      | RS                                                | "1": R = 10 KΩ<br>"0": R= 10Ω            | Ratio selection                                                  |  |

|                 | BIST               | TTL                                      | BIST                                              | "1": R = 10 KΩ<br>"0": R= 10Ω            | Built-in Self Test                                               |  |

|                 | DIODE              | Max:<br>VDiode = 700 mV<br>Idiode = 1 mA | DIODE                                             | Max:<br>VDiode = 700 mV<br>Idiode = 1 mA | Die junction temperature monitoring                              |  |

### 8 Migration from TS81102G0 to AT84CS001

| Туре                       | TS81102G0                      |                                  | AT840        | CS001                         | Description                                  |  |

|----------------------------|--------------------------------|----------------------------------|--------------|-------------------------------|----------------------------------------------|--|

|                            | SwiAdjust                      | 0V ± 0.5V                        | (Suppressed) |                               | Output buffers swing<br>adjustment           |  |

| Synchronization            | AsynchReset                    | TTL                              | ASYNCRST     | LVCMOS/CMOS                   | Asynchronous reset                           |  |

|                            | SynchReset/<br>SynchResetb     | Differential ECL                 | (Suppressed) |                               | Synchronous reset                            |  |

|                            | DMUXDelAdjCtrl                 | 0V ± 0.5V                        | CLKDACTRL    | $V_{CCD}/3$ to $2V_{CCD}/3$   | DMUX clock delay adjust                      |  |

|                            | ADCDelAdjCtrl                  | 0V ± 0.5V                        | DACTRL       | $V_{CCD}/3$ to $2V_{CCD}/3$   | Standalone delay cell<br>adjust              |  |

|                            |                                |                                  | DAEN         | "1": R = 10 KΩ<br>"0": R= 10Ω | Standalone delay cell<br>adjust enable       |  |

|                            | ADCDelAdjln/<br>ADCDelAdjlnb   | Differential ECL                 | DAI/DAIN     | LVDS                          | Stand-alone delay cell<br>adjust input data  |  |

|                            | ADCDelAdjOut/<br>ADCDelAdjOutb | Adjustable<br>Differential logic | DAO/DAON     | LVDS                          | Stand-alone delay cell<br>adjust output data |  |

| Power supplies             | GND                            | 0V                               | DGND         | 0V                            | Common ground                                |  |

|                            | VEE                            | -5V                              | (suppressed) |                               | Digital negative supply                      |  |

|                            | VPLUSD                         | 0V to 3.3V                       | VPLUSD       | 2.5V                          | Digital output supply                        |  |

|                            | VCC                            | 5V                               | VCCD         | 3.3V                          | Digital positive supply                      |  |

| Package top side potential |                                | -5V                              |              | Ground                        |                                              |  |

Table 3. Signal Electrical Levels (Continued)

### **Hardware Implementation**

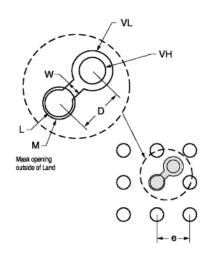

Package CharacteristicsThe TS81102G0 is offered in both TBGA 240 and CQFP 196 packages in order to<br/>address all types of screening, from commercial to military and even space.<br/>The AT84CS001 mainly addresses the commercial and industrial markets and is offered<br/>in an EBGA 240 package, which is quite similar to the TBGA 240.Mechanical characteristicsThe TBGA 240 and EBGA 240 packages have equivalent mechanical characteristics,<br/>permitting use of the same board footprint for both devices.

### Table 4. Main Dimensions of TBGA 240 and EBGA 240 Packages (all Dimensions in Millimeters)

| Parameter                                       |       | TS81102G0 |       |       | AT84CS001 |       |

|-------------------------------------------------|-------|-----------|-------|-------|-----------|-------|

|                                                 | Min   | Тур       | Max   | Min   | Тур       | Max   |

| Body size                                       | 24.80 | 25.00     | 25.20 | 24.80 | 25.00     | 25.20 |

| Height (from bottom of balls to top of package) | 1.30  | 1.50      | 1.70  | 1.25  | 1.45      | 1.60  |

| Ball pitch                                      | 1.27  | 1.27      |       |       | 1.27      |       |

| Ball diameter                                   | 0.60  | 0.75      | 0.90  | 0.70  | 0.80      | 0.90  |

### Table 5. Board Layout Recommendations

| Description                        | Dimensions | Atmel St | andard |

|------------------------------------|------------|----------|--------|

|                                    |            | mm       | mil    |

| Component land pad diameter (pad)  | -          |          |        |

| Solder land diameter               | L          | 0.71     | 28     |

| Diameter of opening in solder mask | М          | 0.71     | 28     |

| Solder (ball) land pitch           | е          | 1.27     | 50     |

| Line width between via and land    | W          | 0.51     | 20     |

| Distance between via and land      | D          | 0.71     | 28     |

| Via land diameter                  | VL         | 0.66     | 26     |

| Through hole diameter              | VH         | 0.38     | 15     |

Figure 7. Board Layout

| Electrical Characteristics | The electrical characteristics of the EBGA 240 are equivalent to those of the TBGA 240.                                                    |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                            | The main advantage of the EBGA 240 is that it provides 4 layers for the power and ground planes, while the TBGA 240 only offers one layer. |

**Thermal Characteristics** The two packages have equivalent thermal characteristics.

| Table 6. Thermal Characteristics of TS81102G0 and AT84CS00 |

|------------------------------------------------------------|

|------------------------------------------------------------|

| Parameter                                                                      | TS81102G0    | AT84CS001    |

|--------------------------------------------------------------------------------|--------------|--------------|

| Rthj-bottom of balls<br>Thermal resistance from junction to<br>bottom of balls | 4.8°C/W      | 5°C/W        |

| Rthj-case<br>Thermal resistance from junction to case                          | 1.40°C/W max | 1.70°C/W max |

| Moisture                                                                       | MLS3         | MSL3         |

Notes: 1. The TS81102G0 package top side (copper heat spreader) is electrically connected to V<sub>EE</sub> = -5V while the AT84CS001 package top side (copper heat spreader) is at 0V.

2. The same heat sink can be used for both devices.

### **Board Implementation**

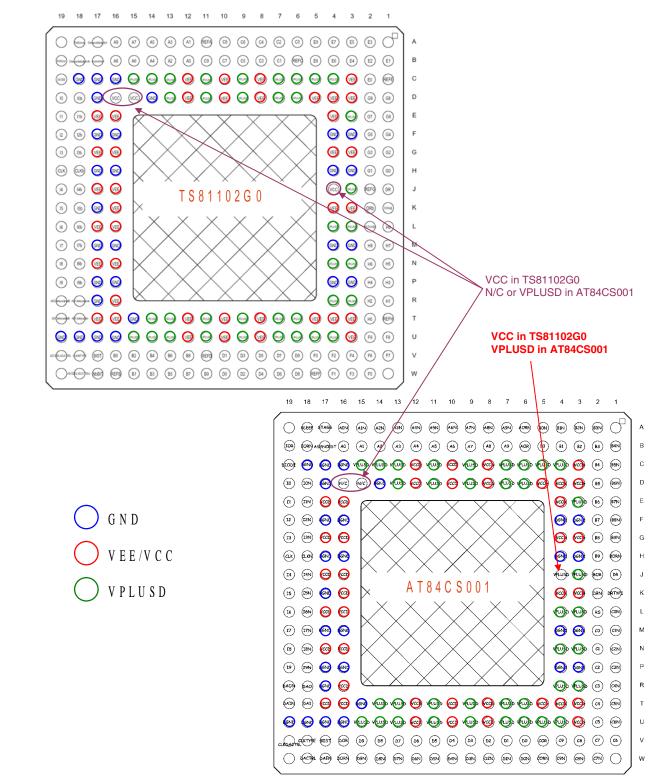

### Power Supplies

In the TS81102G0 device, it was necessary to use three power supplies (or even four in some cases):  $V_{EE} = -5V$ ,  $V_{CC} = 5V$  and  $V_{PLUSD} = 0V$  to 3.3V depending on the required output levels (and  $V_{TT} = -2V$  to 1.3V depending on the application).

With the AT84CS001 DMUX, only two power supplies are now necessary:  $V_{CCD} = 3.3V$  and  $V_{PLUSD} = 2.5V$ .

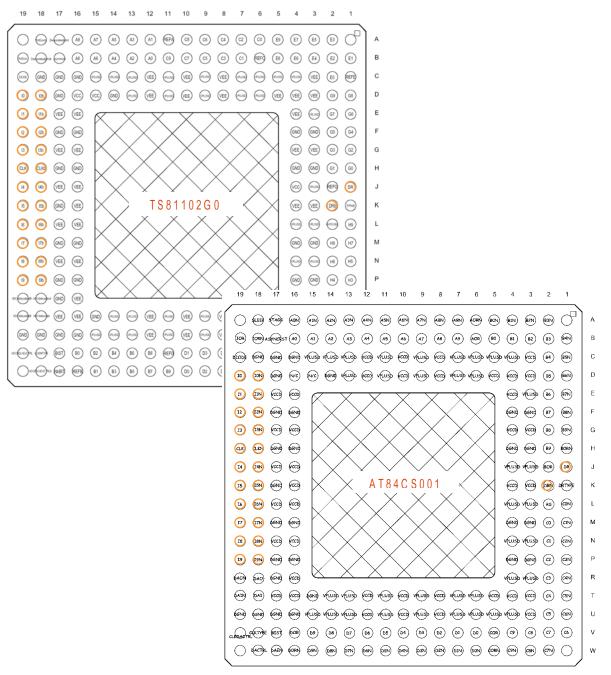

To simplify migration from the TS81102G0 to the AT84CS001, all the pins used for power supplies in the first device are also used as power pins in the second.

The pins formerly used for V<sub>EE</sub> in the TS81102G0 are now used for V<sub>CCD</sub> in the AT84CS001, thus enabling you to keep the same layer for the V<sub>CC</sub> power supply as for the former V<sub>EE</sub>.

The pins used formerly for  $V_{PLUSD}$  in the TS81102G0 are still used for  $V_{PLUSD}$  in the AT84CS001, also enabling you to keep the same layer for the  $V_{PLUSD}$  power supply.

The V<sub>CC</sub> power supply of the TS81102G0 is replaced by 2 "N/C" (no connect) pins on D15 and D16 but pin J4 becomes V<sub>PLUSD</sub> in the AT84CS001.

Since pins D15 and D16 are not connected to the AT84CS001 device, it is possible to connect them to  $V_{PLUSD}$  = 2.5V so as to simplify layout (the  $V_{CC}$  plane in TS81102G0 becomes  $V_{PLUSD}$ ).

Finally, the same ground pins are used in both designs.

Table 7.

Power Supplies Pin Assignment

| Pin Number                                                                                                                                                                               | TS81102G0 Signal name | AT84CS001 Signal Name              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------|

| C12, C10, C8, C3, D12, D10, D8, D5, D4,<br>D3, E17, E16, G17, G16, G4, G3, J17,<br>J16, K16, K4, K3, L17, L16, N17, N16,<br>R16, T17, T16, T12, T10, T8, T5, T4, T3,<br>U12, U10, U8, U3 | VEE                   | VCCD                               |

| C18, C17, C16, D17, D14, F17, F16, F4,<br>F3, H17, H16, H4, H3, K17, M17, M16,<br>M4, M3, P17, P16, P4, P3, R17, T15, U19,<br>U18, U17, U16                                              | GND                   | DGND                               |

| C15, C14, C13, C11 C9, C7, C6, C5, C4,<br>D13, D11, D9, D7, D6, E3, J4, J3, L4, L3,<br>N4, N3, R4, R3, T14, T13, T11, T9, T7,<br>T6, U15, U14, 13, U11, U9, U7, U6, U5,<br>U4            | VPLUSD                | VPLUSD                             |

| D15, D16                                                                                                                                                                                 | VCC                   | N/C but can be connected to VPLUSD |

| J4                                                                                                                                                                                       | VCC                   | VPLUSD                             |

#### Figure 8. Matching of Power Pins on TS81102G0 and AT84CS001 Devices

### Input Data, Input and Output Clock Signals

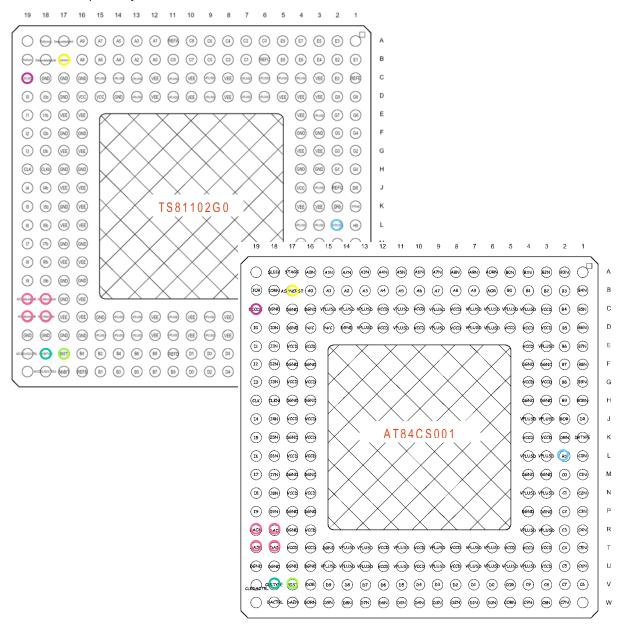

The 10-bit input data from I0/I0b to I9/I9b (I0/I0N to I9/I9N in the AT84CS001), the input clock CLK/CLKb (or CLK/CLKN in the AT84CS001) as well as the output clock DR/DRb (DR/DRN in the AT84CS001) are assigned the same pins in both devices.

This implies that the same board layout for these signals can be maintained.

Table 8. Input Data, Input and Output Clock Pin Assignment

| Signal name                  | TS81102G0 Pin Number                                | AT84CS001 Pin Number                                |  |

|------------------------------|-----------------------------------------------------|-----------------------------------------------------|--|

| 1019                         | D19, E19, F19, G19, J19,<br>K19, L19, M19, N19, P19 | D19, E19, F19, G19, J19,<br>K19, L19, M19, N19, P19 |  |

| I0bI9b (I0NI9N)              | D18, E18, F18, G18, J18,<br>K18, L18, M18, N18, P18 | D18, E18, F18, G18, J18,<br>K18, L18, M18, N18, P18 |  |

| CLK/CLKb (CLK/CLKN) H19, H18 |                                                     | H19, H18                                            |  |

| DR/DRb (DR/DRN)              | J1, K2                                              | J1, K2                                              |  |

#### Figure 9. Input Data, Input and Output Clock Pinout

### **Other Functions**

| Table 9. Pinout Compatibility of Other Function |

|-------------------------------------------------|

|-------------------------------------------------|

| Pin Number | TS81102G0 Signal name | AT84CS001 Signal name |  |

|------------|-----------------------|-----------------------|--|

| C19        | DIODE                 | DIODE                 |  |

| B17        | Asyncreset            | ASYNCRST              |  |

| V18        | CLKINTYPE             | CLKTYPE               |  |

| R18        | ADCDelAdjOut          | DAO                   |  |

| R19        | ADCDelAdjOutb         | DAON                  |  |

| T18        | ADCDelAdjIn           | DAI                   |  |

| Т19        | ADCDelAdjInb          | DAIN                  |  |

| L2         | RATIOSEL              | RS                    |  |

| V17        | BIST                  | BIST                  |  |

#### Figure 10. Pinout Compatibility of Other Functions

## Summary of Pinout Compatibility

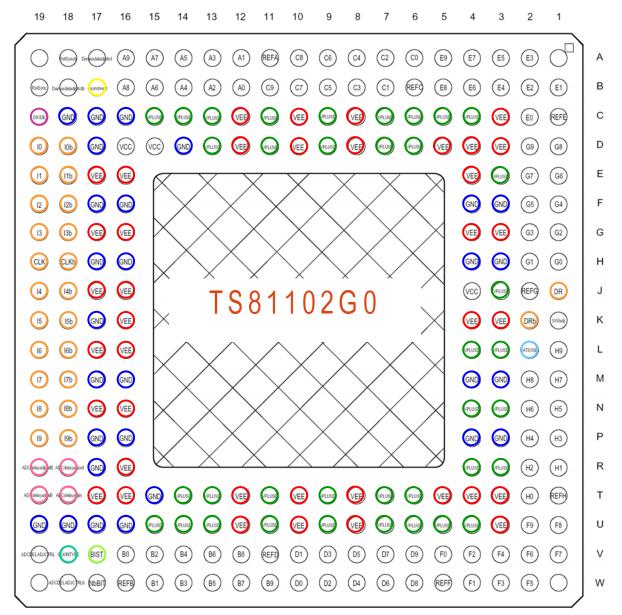

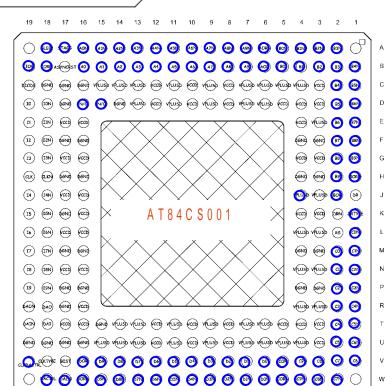

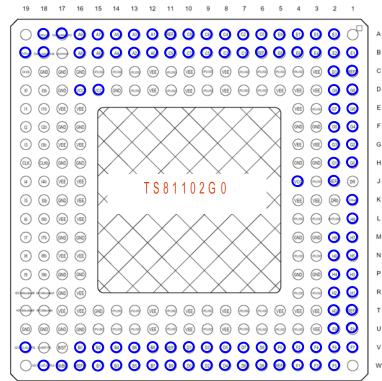

#### Figure 11. TS81102G0 Pinout

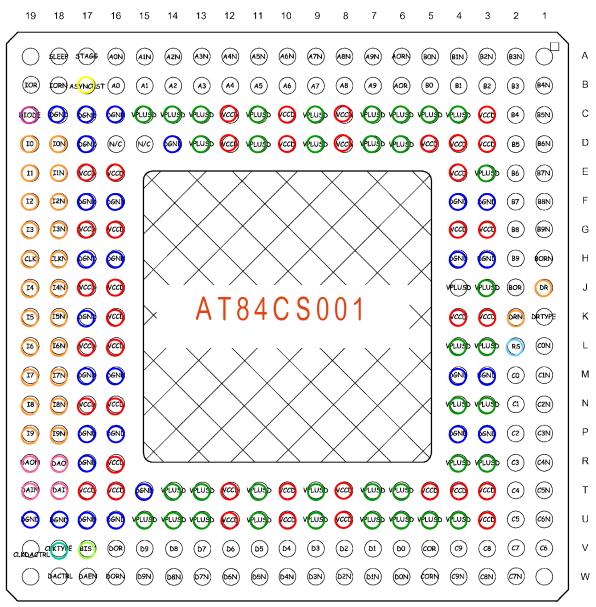

#### Figure 12. AT84CS001 Pinout

### Summary of Differences in Layout

| Pin<br>Number | TS81102G0 Signal<br>Name | AT84CS001 Signal<br>Name | Pin<br>Number | TS81102G0 Signal<br>Name | AT84CS001 Signal<br>Name |

|---------------|--------------------------|--------------------------|---------------|--------------------------|--------------------------|

| B19           | RstSync                  | IOR                      | L1            | H9                       | CON                      |

| A18           | RstSyncb                 | SLEEP                    | M2            | H8                       | C0                       |

| A17           | Demuxdeladjctrl          | STAGG                    | M1            | H7                       | C1N                      |

| B18           | Demuxdeladjctrlb         | IORN                     | N2            | H6                       | C1                       |

| A16           | A9                       | AON                      | N1            | H5                       | C2N                      |

| B16           | A8                       | A0                       | P2            | H4                       | C2                       |

| A15           | A7                       | A1N                      | P1            | H3                       | C3N                      |

| B15           | A6                       | A1                       | R2            | H2                       | C3                       |

| A14           | A5                       | A2N                      | R1            | H1                       | C4N                      |

| B14           | A4                       | A2                       | T2            | HO                       | C4                       |

| A13           | A3                       | A3N                      | T1            | RefH                     | C5N                      |

| B13           | A2                       | A3                       | U2            | F9                       | C5                       |

| A12           | A1                       | A4N                      | U1            | F8                       | C6N                      |

| B12           | A0                       | A4                       | V1            | F7                       | C6                       |

| A11           | RefA                     | A5N                      | V2            | F6                       | C7                       |

| B11           | C9                       | A5                       | W2            | F5                       | C7N                      |

| A10           | C8                       | A6N                      | V3            | F4                       | C8                       |

| B10           | C7                       | A6                       | W3            | F3                       | C8N                      |

| A9            | C6                       | A7N                      | V4            | F2                       | C9                       |

| B9            | C5                       | A7                       | W4            | F1                       | C9N                      |

| A8            | C4                       | A8N                      | V5            | F0                       | COR/DRCN                 |

| B8            | C3                       | A8                       | W5            | RefF                     | CORN/DRC                 |

| A7            | C2                       | A9N                      | V6            | D9                       | D0                       |

| B7            | C1                       | A9                       | W6            | D8                       | DON                      |

| A6            | C0                       | AORN/DRA                 | V7            | D7                       | D1                       |

| B6            | RefC                     | AOR/DRAN                 | W7            | D6                       | D1N                      |

| A5            | E9                       | BON                      | V8            | D5                       | D2                       |

| B5            | E8                       | B0                       | W8            | D4                       | D2N                      |

| A4            | E7                       | B1N                      | V9            | D3                       | D3                       |

| B4            | E6                       | B1                       | W9            | D2                       | D3N                      |

| A3            | E5                       | B2N                      | V10           | D1                       | D4                       |

| B3            | E4                       | B2                       | W10           | D0                       | D4N                      |

| A2            | E3                       | B2                       | V11           | RefD                     | D5                       |

| B2            | E2                       | B3                       | W11           | B9                       | D5N                      |

Table 10. Pin Differences between TS81102G0 and AT84CS001

### <sup>20</sup> Migration from TS81102G0 to AT84CS001

| Pin<br>Number | TS81102G0 Signal<br>Name | AT84CS001 Signal<br>Name | Pin<br>Number | TS81102G0 Signal<br>Name | AT84CS001 Signal<br>Name |

|---------------|--------------------------|--------------------------|---------------|--------------------------|--------------------------|

| B1            | E1                       | B4N                      | V12           | B8                       | D6                       |

| C2            | E0                       | B4                       | W12           | B7                       | D6N                      |

| C1            | RefE                     | B5N                      | V13           | B6                       | D7                       |

| D2            | G9                       | B5                       | W13           | B5                       | D7N                      |

| D1            | G8                       | B6N                      | V14           | B4                       | D8                       |

| E2            | G7                       | B6                       | W14           | B3                       | D8N                      |

| E1            | G6                       | B7N                      | V15           | B2                       | D9                       |

| F2            | G5                       | B7                       | W15           | B1                       | D9N                      |

| F1            | G4                       | B8N                      | V16           | B0                       | DOR/DRDN                 |

| G2            | G3                       | B8                       | W16           | RefB                     | DORN/DRD                 |

| G1            | G2                       | B9N                      | J4            | VCC                      | VPLUSD                   |

| H2            | G1                       | B9                       | K1            | SWladj                   | DRTYPE                   |

| H1            | G0                       | BORN/DRB                 | W17           | NbBIT                    | DAEN                     |

| J2            | RefG                     | BOR/DRBN                 | V19           | ADCDELADJCTRL            | CLKDACTRL                |

| D15, D16      | VCC                      | N/C or VPLUSD            | W18           | ADCDELADJCTRLb           | DACTRL                   |

| Table 10 | Pin Differences betwee | n TS81102G0 and      | AT84CS001 | (Continued) |

|----------|------------------------|----------------------|-----------|-------------|

|          |                        | 11 1 30 1 102 00 anu | A10403001 |             |

### <sup>22</sup> Migration from TS81102G0 to AT84CS001

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

*Memory* 2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corportion 2005. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks, and Everywhere You Are<sup>SM</sup> and others are trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.